- Tác giả Lynn Donovan donovan@answers-technology.com.

- Public 2023-12-15 23:55.

- Sửa đổi lần cuối 2025-01-22 17:46.

VHDL và Verilog được coi là ngôn ngữ thiết kế kỹ thuật số có mục đích chung, trong khi SystemVerilog đại diện cho phiên bản không được nâng cấp của Verilog . VHDL có rễ bên trong Ngôn ngữ lập trình Ada ở cả khái niệm và cú pháp, trong khi Verilog's root có thể được theo dõi trở lại HDL ban đầu được gọi làHilo và ngôn ngữ lập trình C.

Mọi người cũng hỏi, VHDL hay Verilog tốt hơn?

VHDL dài dòng hơn Verilog và itis cũng có cú pháp không giống C. Với VHDL , bạn có cơ hội viết nhiều dòng mã hơn. Verilog có một tốt hơn nắm bắt mô hình phần cứng, nhưng có mức độ cấu trúc lập trình thấp hơn. Verilog không dài dòng như VHDL vì vậy đó là lý do tại sao nó nhỏ gọn hơn.

Ngoài ra, việc sử dụng Verilog là gì? Verilog là một Ngôn ngữ Mô tả Phần cứng; định dạng atextual để mô tả các mạch và hệ thống điện tử. Áp dụng cho thiết kế điện tử, Verilog được sử dụng để xác minh thông qua mô phỏng, phân tích thời gian, phân tích thử nghiệm (phân tích khả năng kiểm tra và phân loại lỗi) và để tổng hợp logic.

Theo cách này, sự khác biệt giữa Verilog và SystemVerilog là gì?

Chính sự khác biệt giữa Verilog vàSystemVerilog đó là Verilog là một Mô tả Phần cứng Ngôn ngữ, trong khi SystemVerilog là Ngôn ngữ Mô tả Phần cứng và Ngôn ngữ Xác minh Phần cứng dựa trên Verilog . Tóm lại, SystemVerilog là một phiên bản nâng cao của Verilog các tính năng bổ sung.

VHDL trong VLSI là gì?

VLSI Thiết kế - VHDL Giới thiệu. Quảng cáo. VHDL là viết tắt của ngôn ngữ mô tả phần cứng mạch tích hợp tốc độ rất cao. Nó là một ngôn ngữ lập trình được sử dụng để lập mô hình hệ thống kỹ thuật số theo luồng dữ liệu, hành vi và phong cách cấu trúc của mô hình hóa.

Đề xuất:

Sự khác biệt giữa Pebble Tec và Pebble Sheen là gì?

Pebble Tec được làm từ những viên đá cuội tự nhiên, được đánh bóng tạo ra kết cấu mấp mô và bề mặt không trơn trượt. Pebble Sheen kết hợp công nghệ tương tự như Pebble Tec, nhưng sử dụng các viên sỏi nhỏ hơn để có lớp hoàn thiện bóng bẩy

Sự khác biệt giữa một nhà tâm lý học nhận thức và một nhà khoa học thần kinh nhận thức là gì?

Tâm lý học nhận thức tập trung hơn vào việc xử lý thông tin và hành vi. Khoa học thần kinh nhận thức nghiên cứu sinh học cơ bản của quá trình xử lý thông tin và hành vi. khoa học thần kinh nhận thức ở trung tâm

Sự khác biệt giữa lắp ráp và tháo rời là gì?

Là assembly là (tính toán) trong microsoft net, một khối xây dựng của ứng dụng, tương tự như dll, nhưng chứa cả mã thực thi và thông tin thường được tìm thấy trong thư viện kiểu của dll, thông tin thư viện kiểu trong một assembly, được gọi là tệp kê khai, mô tả chức năng công khai, dữ liệu, lớp và phiên bản

Sự khác biệt giữa các công tắc Cherry MX màu khác nhau là gì?

Cherry MX Red switch tương tự như Cherry MX Blacks ở điểm cả hai đều được phân loại là tuyến tính, không xúc giác. Điều này có nghĩa là cảm giác của họ không đổi qua mỗi hành trình phím lên-xuống. Điểm khác biệt của chúng với các công tắc Cherry MX Black là khả năng chống chịu của chúng; họ cần ít lực hơn để hành động

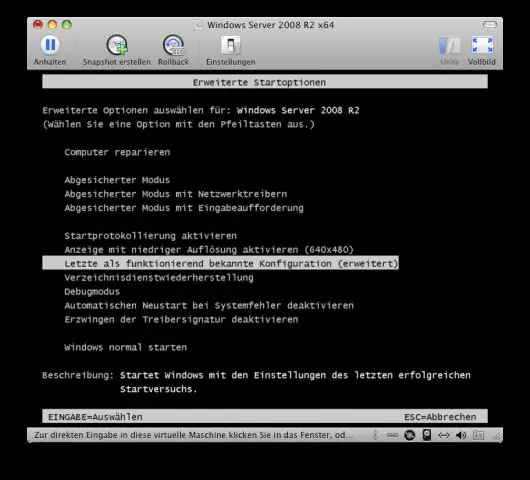

Sự khác biệt giữa cấu hình tốt được biết đến gần đây nhất và khôi phục hệ thống là gì?

Trong khi Khôi phục Hệ thống sử dụng các điểm khôi phục để đưa các tệp và cài đặt hệ thống của bạn về thời điểm trước đó mà không ảnh hưởng đến các tệp cá nhân. Bạn có thể hoàn tác khôi phục hệ thống nhưng không có tùy chọn như vậy trong Cấu hình Tốt Được biết Cuối cùng. Cấu hình tốt được biết đến gần đây nhất bị tắt trong Windows 8 hoặc Windows 8.1 theo mặc định